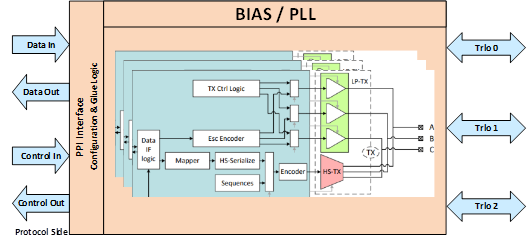

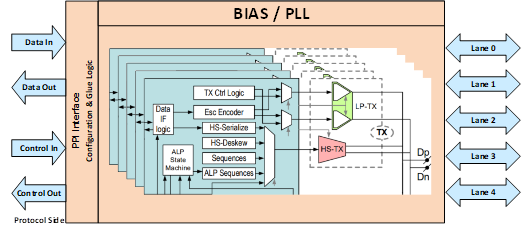

MIPI D-PHY is a serial interface technology which is widely adopted in smartphones and other multimedia enabled mobile devices. To further improve throughput over bandwidth limited channel, the C-PHY is developed and is delivering 2.28 bits per symbol over three-wire trio. As a MIPI Alliance contributor and leading Interface IP provider, M31 provides a silicon-proven, low-power and low cost C-PHY/D-PHY combo IP on various process nodes. Users can configure the PHY into D-PHY mode or C-PHY mode to support different applications using the same PHY. It is compliant to the PPI interface which allows seamless integration with upside controllers for Camera Serial Interface (CSI-2) and Display Serial Interface (DSI) protocols.

- IP Product Lists

- C-PHY v2.0 / D-PHY v2.5 Features

- C-PHY v1.2 / D-PHY v1.2 Features

- Compliant with MIPI D-PHY v2.5 and C-PHY v2.0 specifications

- Supports MIPI DSI and CSI-2 protocols

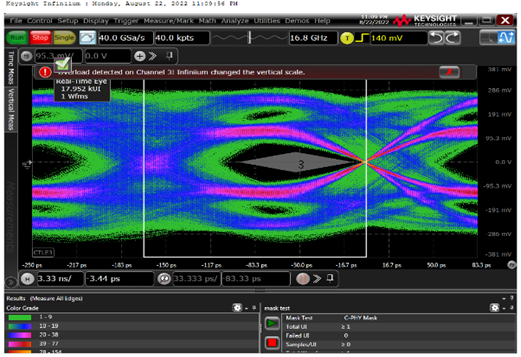

- Supports HS data rates up to 6Gbps (6Gsps) per lane (per trio)

- Supports LS data rate of 10Mbps and Ultra-low power modes

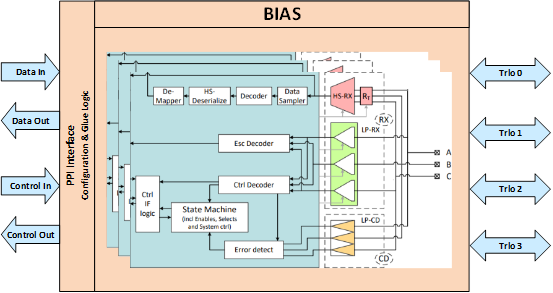

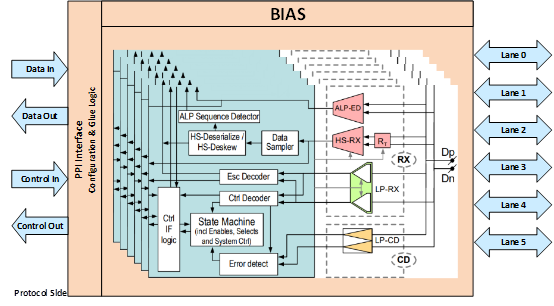

- Supports D-PHY mode with 1 clock lane & up to 4 data lanes

- Supports C-PHY mode up to 3 trios for TX and 4 trios for RX

- Supports extra RX mode with 2 sets of 1 clock lane & up to 2 data lanes

- Supports Alternate Low-Power (ALP) mode

- Provides D-PHY swap function for clock and data lane

- Provides C-PHY swap function for trio

- Provides a stand-alone BIST module for at-speed mass production testing

- Certified with ASIL-B of ISO-26262

- Compliant with MIPI D-PHY v1.2 and C-PHY v1.2 specs

- Support both MIPI DSI and CSI-2 protocols

- Support HS data rate from 80Mbps (0.8Gsps) up to 2.5Gbps (3.5Gsps) per lane (per trio)

- Support LS data rate of 10Mbps and Ultra-low power mode

- Support D-PHY mode with 1 clock lane & up to 4 data lanes

- Support C-PHY mode up to 3 trios for TX and 4 trios for RX

- Support TX-EQ function to compensate loss of a long channel

- Support additional D-PHY RX mode with 2 sets of (1 clock lane and up to 2 data lanes)

- Support additional C-PHY RX mode with 2 sets of 2 trios

- Provide D-PHY clock and data lane swap function

- Provide C-PHY trios swap function

- Provide a stand-alone at-speed multi-lanes (trios) parallel BIST module for mass production tests