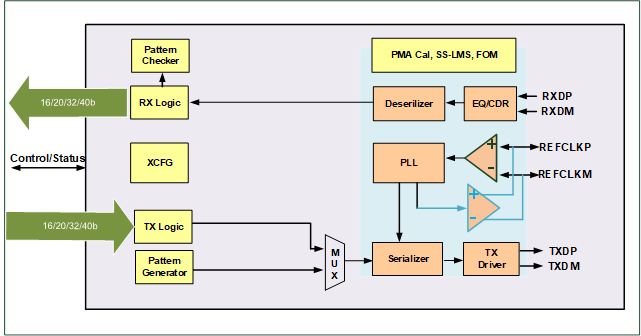

M31 Serdes PHY IP provides high-performance, multi-lane capability and low power architecture for the high-bandwidth applications. The Serdes IP supports data rates from 1.25G to 10.3125Gbps including XFI, SFI, 10GBASE-KR, CEI, XAUI, USXGMII, QSGMII, and SGMII. With the supports for both TX and RX equalization techniques, the Serdes IP is designed to meet the requirements for different channel conditions.

- IP Product Lists

- Features

- Supports 1.25G to 10.3125Gbps data rates and compact die area

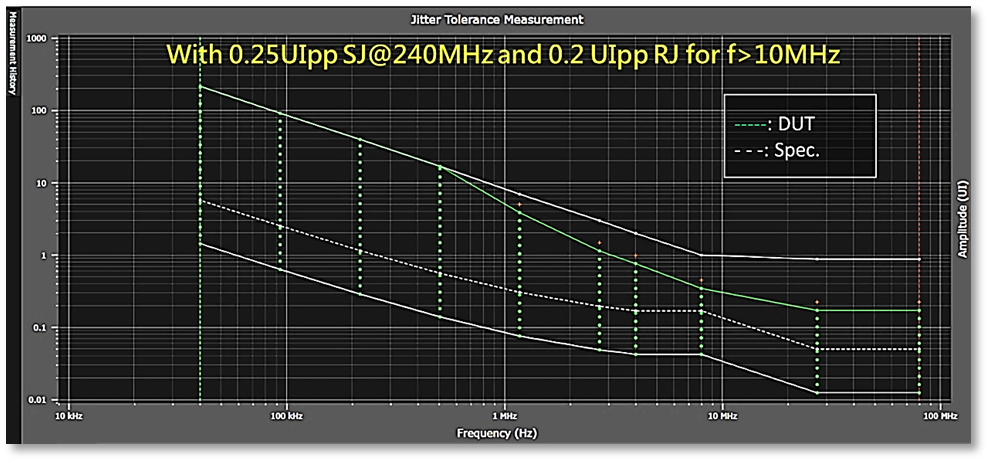

- Supports up to 25dB channel loss@ 5.15625GHz

- Supports RX loss-of-signal detection

- Supports X1, X2 and X4 lanes

- Accessible register controls allow user specific optimization of critical parameters (e.g., TXPLL bandwidth, TX de-emphasis level, CDR bandwidth, and EQ strength)

- Supports both FOM for Link-EQ Training

- Supports robust BIST functions for mass production testing

- Support Wire-Bond and Flip-Chip packages