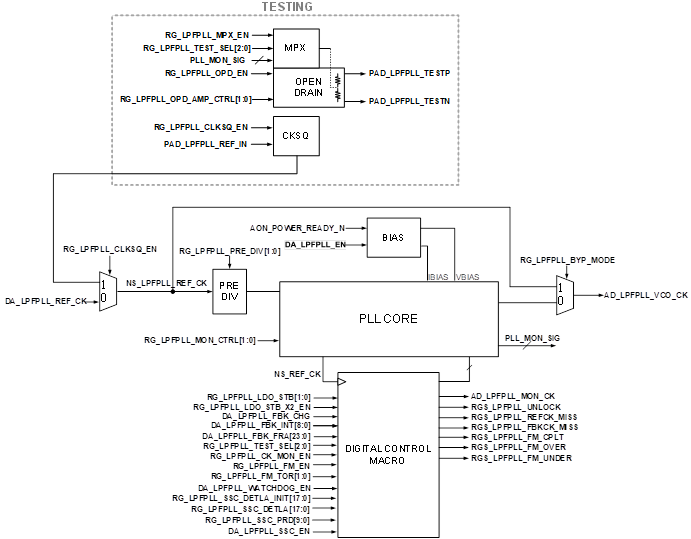

Low Power Fractional PLL is a general purpose frequency synthesizer with an input reference frequency range from 10 to 240 MHz and 3:1 output frequency range. The PLL core is a typical Type-II PLL and the fractional portion of the output frequency is achieved by using a programmable 3rd-ord sigma delta modulator. The PLL core operates on IO supply voltage for excellent supply rejection in noisy SoC applications. It is designed for easy usage and simple integration, eliminating the need for complex configurations.

- IP Product Lists

- Features

- Supports wide input frequency range: 10MHz to 240MHz

- Supports 3:1 output frequency range allows optimization for power and jitter performance

- 24-bit fractional accuracy

- Supports Spread Spectrum Clocking

- Lock Detect Signal indicates when frequency lock is achieved

- Embedded frequency meter circuit for mass production testing

- Embedded continuous monitoring watchdog circuit for automotive applications

- Output mux for bypass mode

- PLL Core Area less than 100µm x 100µm @22nm

- Low Power Consumption, less than 1.0mA from IO voltage domain at lowest output frequency operation