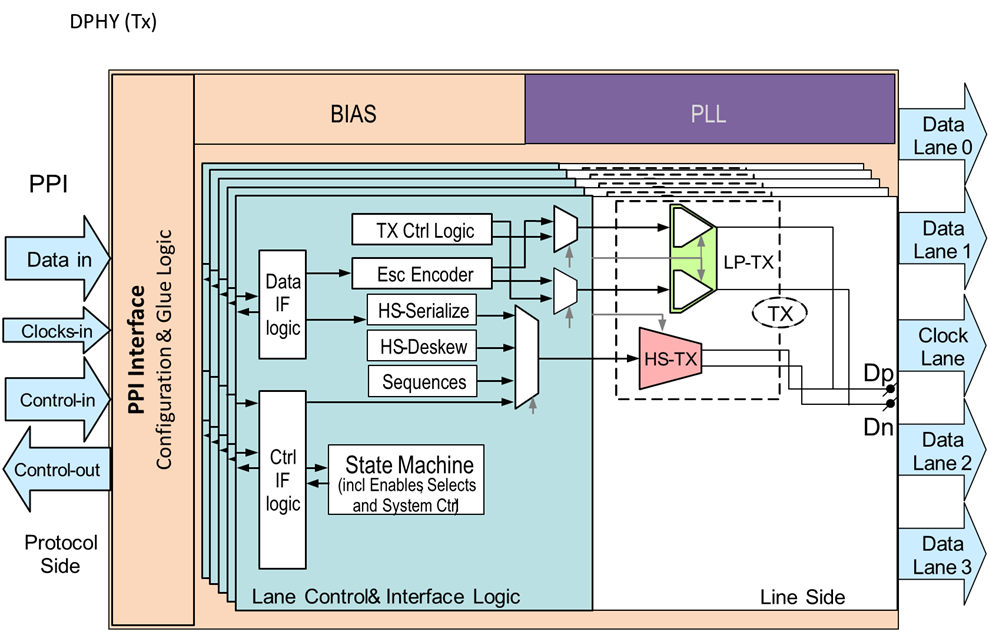

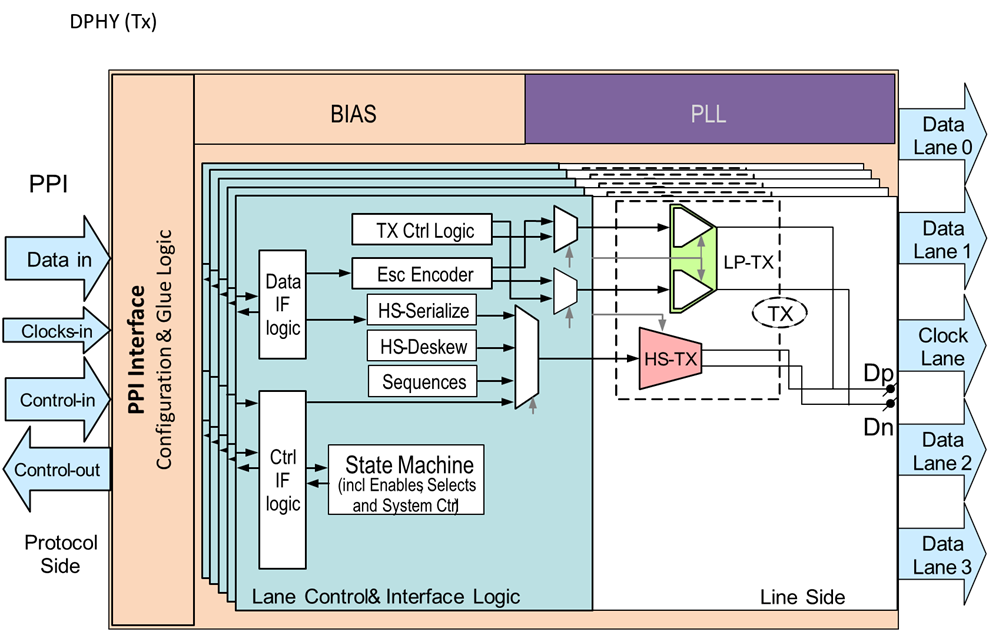

The D-PHY is a popular MIPI physical layer developed for mobile applications because it is a flexible, high-speed, low-power and low-cost solution. As a MIPI Alliance contributor and leading Interface IP provider, M31 provides silicon-proven D-PHY in various process nodes. The D-PHY IP follows MIPI D-PHY v1.2/v1.1 spec and supports a wide range of high-speed (HS) and low-power (LP) data transfers. It is compliant to the PPI interface which allows seamless integration with upside controllers for Camera Serial Interface (CSI-2) and Display Serial Interface (DSI) protocols. Car manufacturers are also adopting MIPI specifications because the solutions are mature, relatively simple to use. M31 provides certified and compact PHY to support automotive applications.

- IP Product Lists

- Features

- Compliant with MIPI D-PHY specification up to v1.2/v1.1 (by different process nodes)

- Supports MIPI DSI and CSI-2 protocols

- Supports HS data rates up to 2.5Gbps (v1.2, per lane) . 1.5Gbps(v1.1, per lane)

- Supports LS data rate of 10Mbps and Ultra-low power modes

- Supports 1 clock lane & up to 4 data lanes

- Supports extra RX mode with 2 sets of 1 clock lane & up to 2 data lanes

- Provides swap function for clock and data lane to ease PCB design

- Provides a stand-alone BIST module for at-speed mass production testing

- Certified with ASIL-B of ISO-26262